# BENHA UNIVERSITY FACULTY OF ENGINEERING AT SHOUBRA

ECE-322 Electronic Circuit (B)

Lecture #11

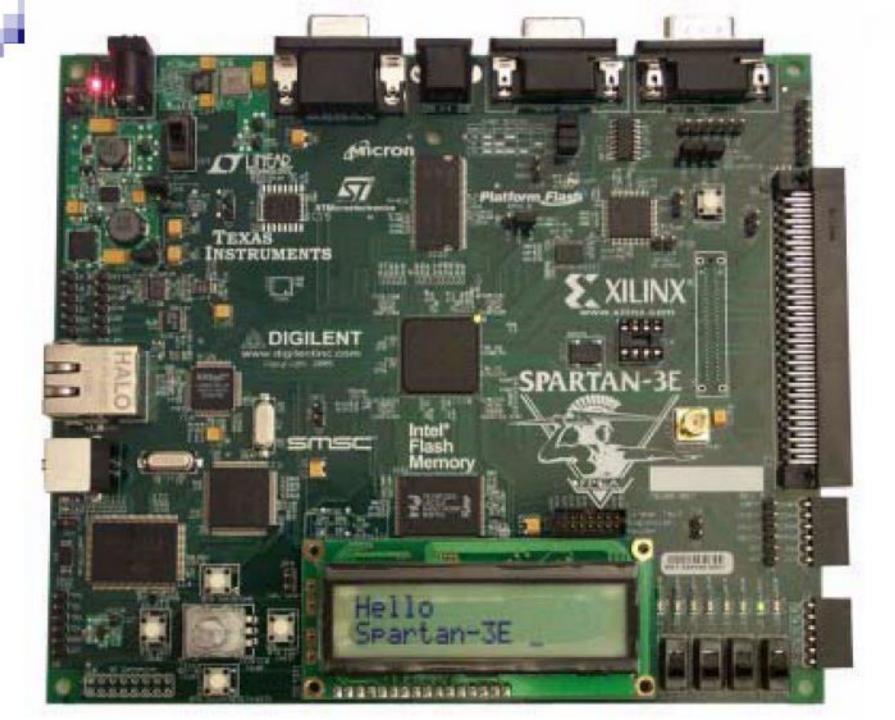

Programming the Spartan-3E

FPGA Board

Instructor:

**Dr. Ahmad El-Banna**

Why Spartan-3E?

Step by Step Example

# Why Spartan-3E?

- Simply, it is available in our lab 😊

- Technically,

- It's one of 5 platforms each delivering a unique cost-optimized balance of programmable logic, connectivity, and dedicated hard IP for your low-cost applications.

- It is used for Logic Optimized applications.

- For applications where logic densities matter more than I/O count Ideal for logic integration, DSP co-processing and embedded control, requiring significant processing and narrow or few interfaces

#### Lecture Reference

We will follow the presentation talks about:

#### "How to program the FPGA SPARTAN-3E Board"

- By anonymous.

- Found at:

- http://web.ewu.edu/groups/technology/Claudio/ee360/Protected/P resentationFPGA.pdf

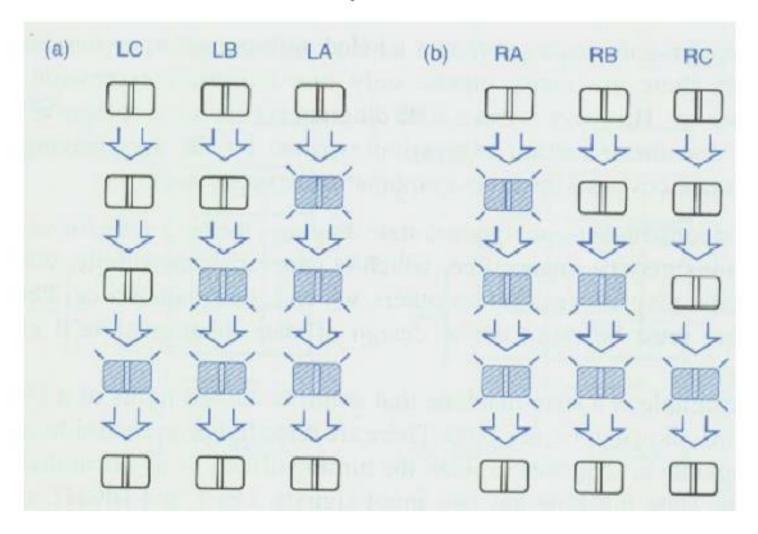

The goal of the project is to write vhdl code to control the tail lights of a 1965 Ford Thunderbird and

then load this code into Spartan-3E FPGA Xilinx Board.

# m

#### **FPGA**

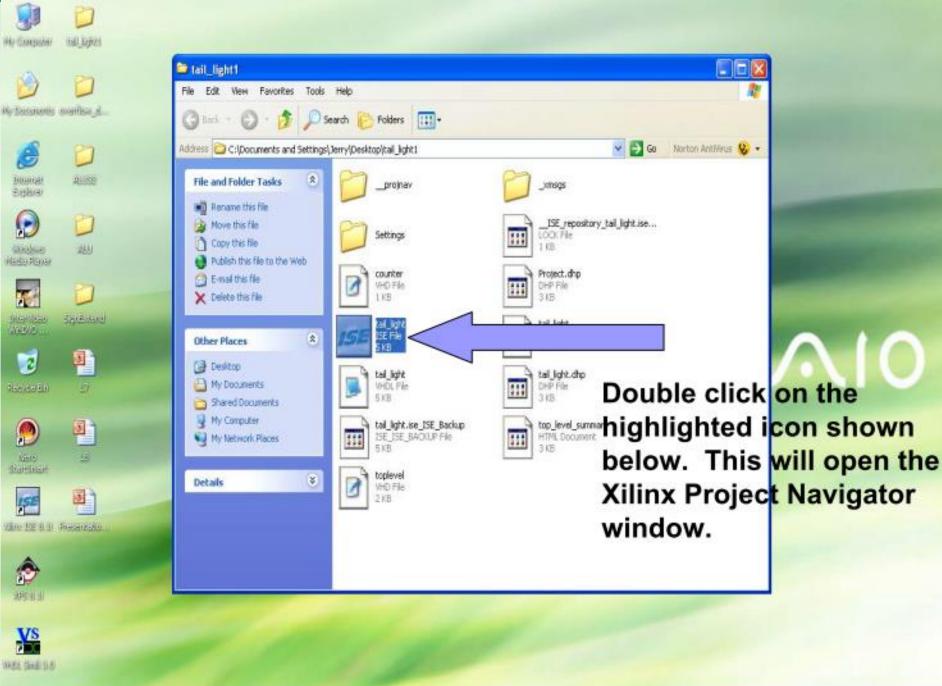

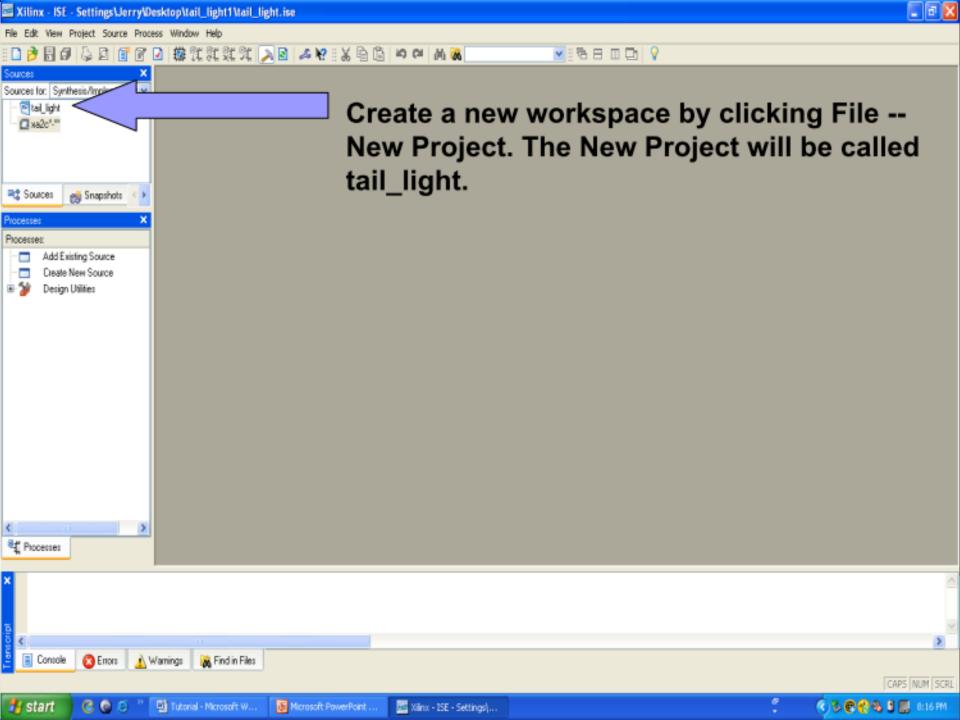

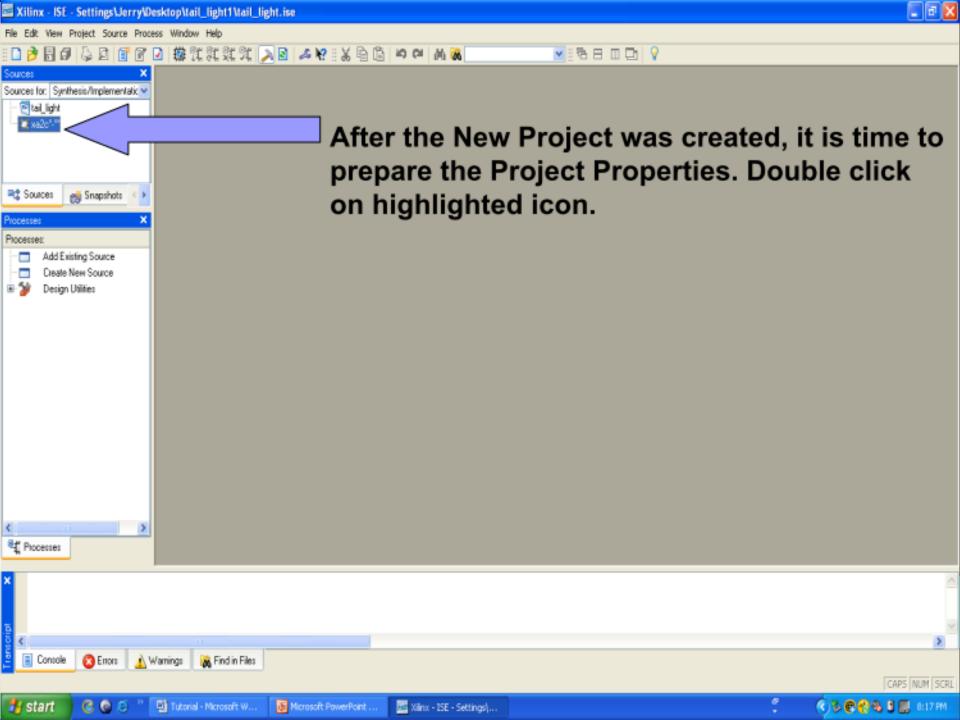

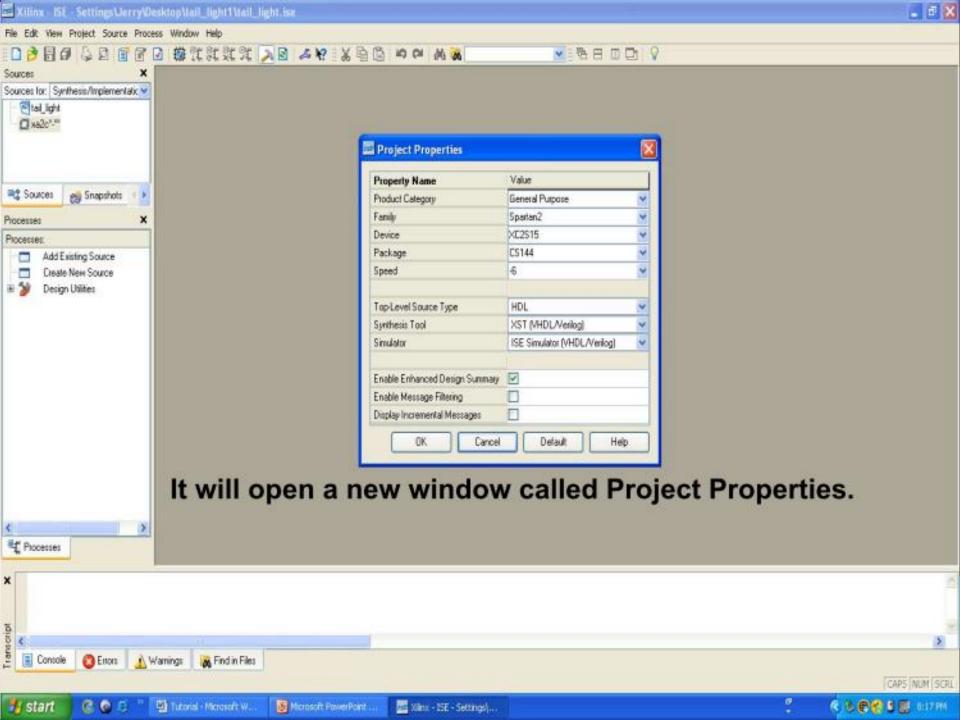

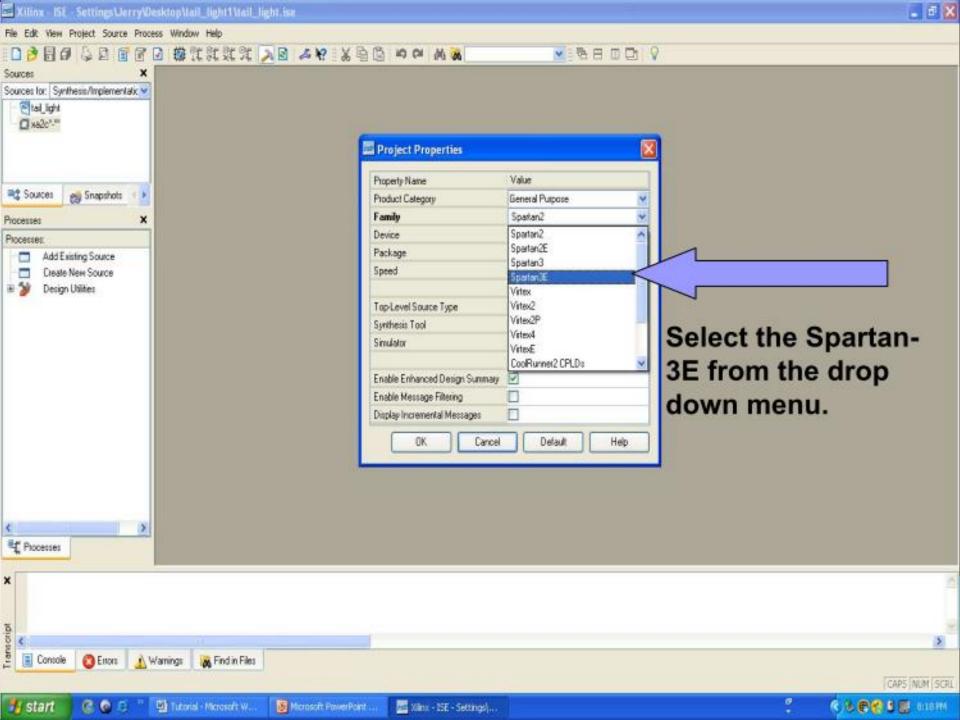

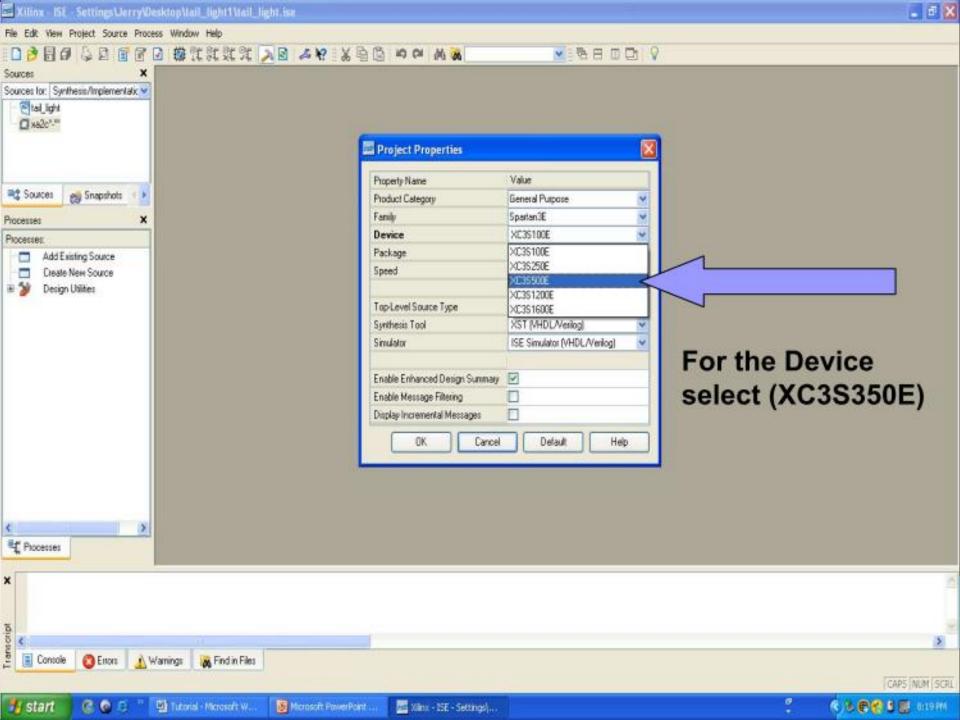

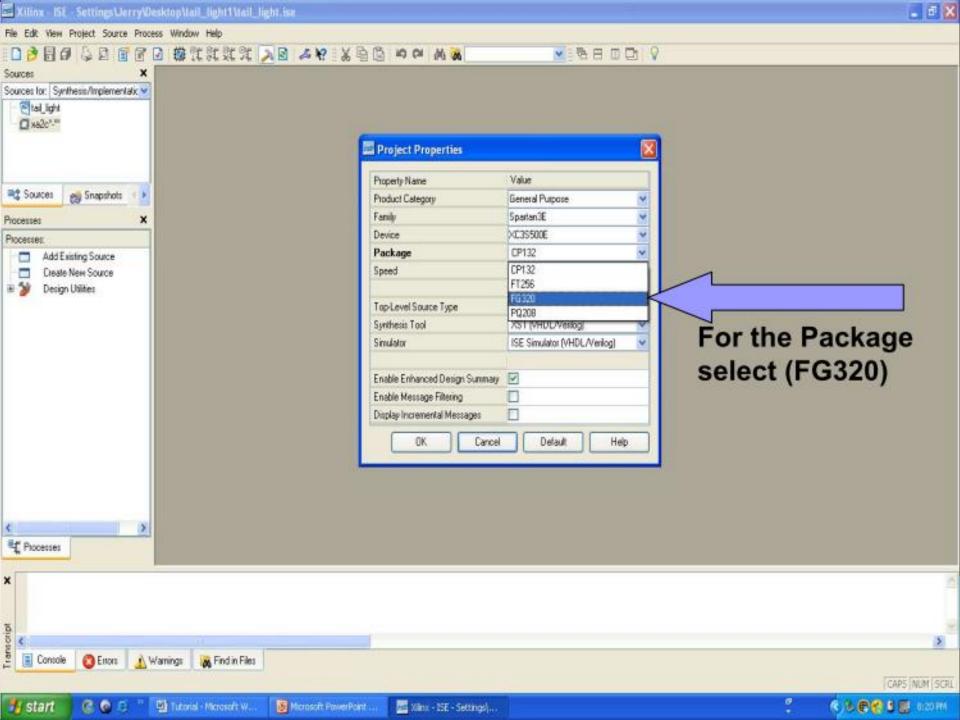

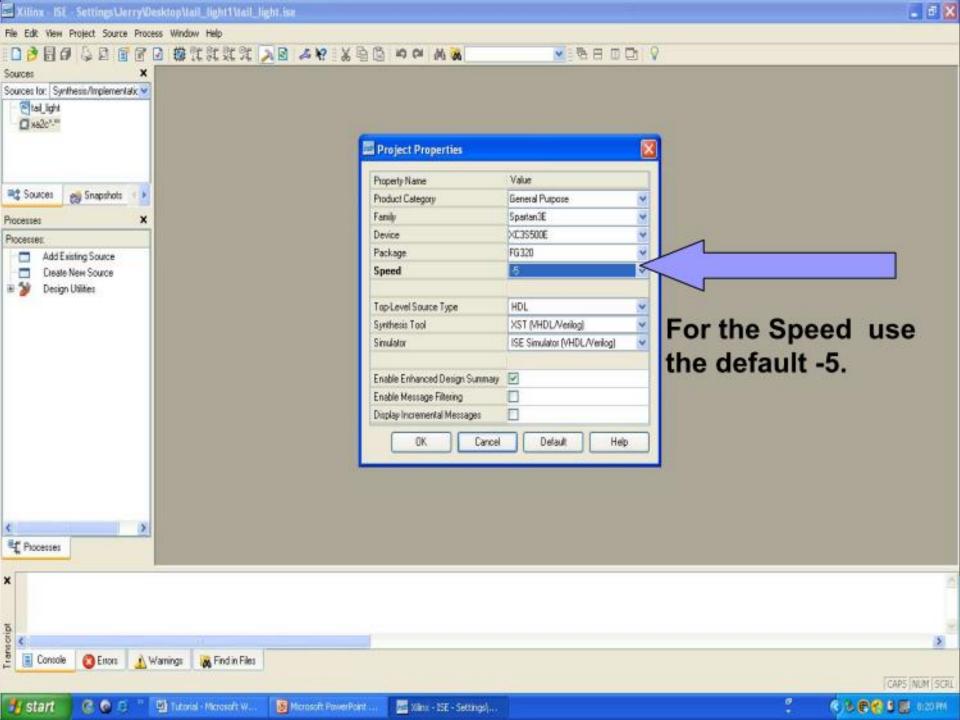

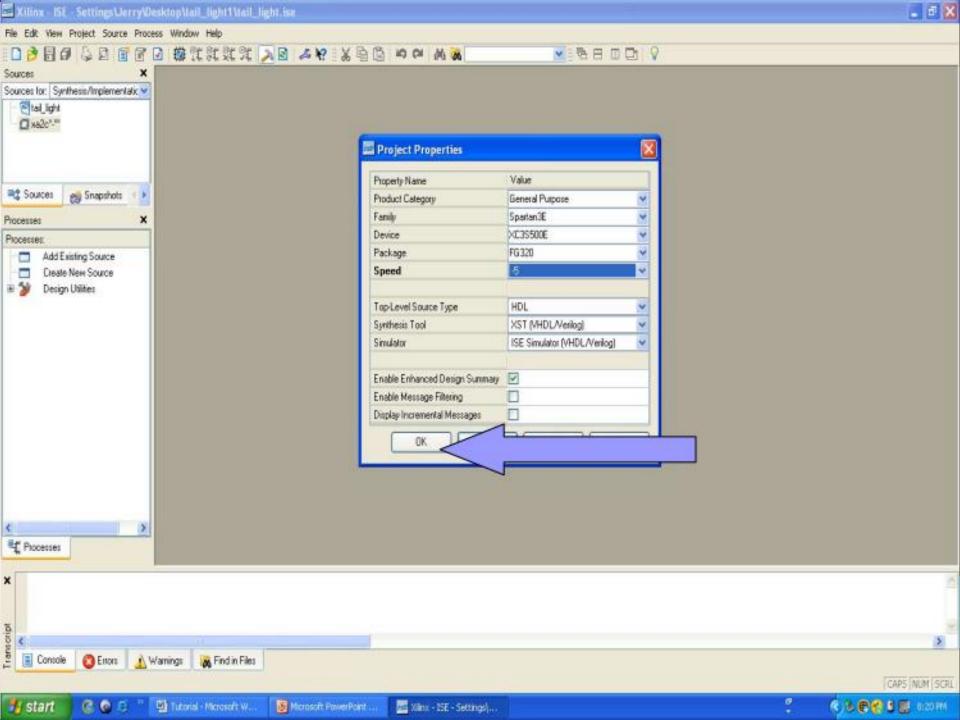

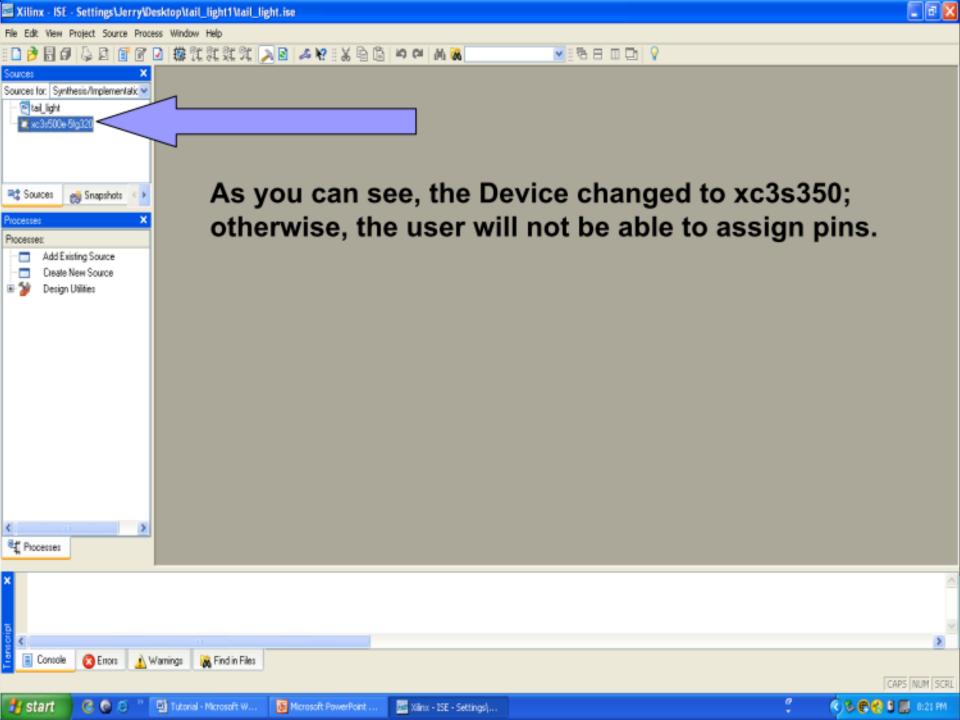

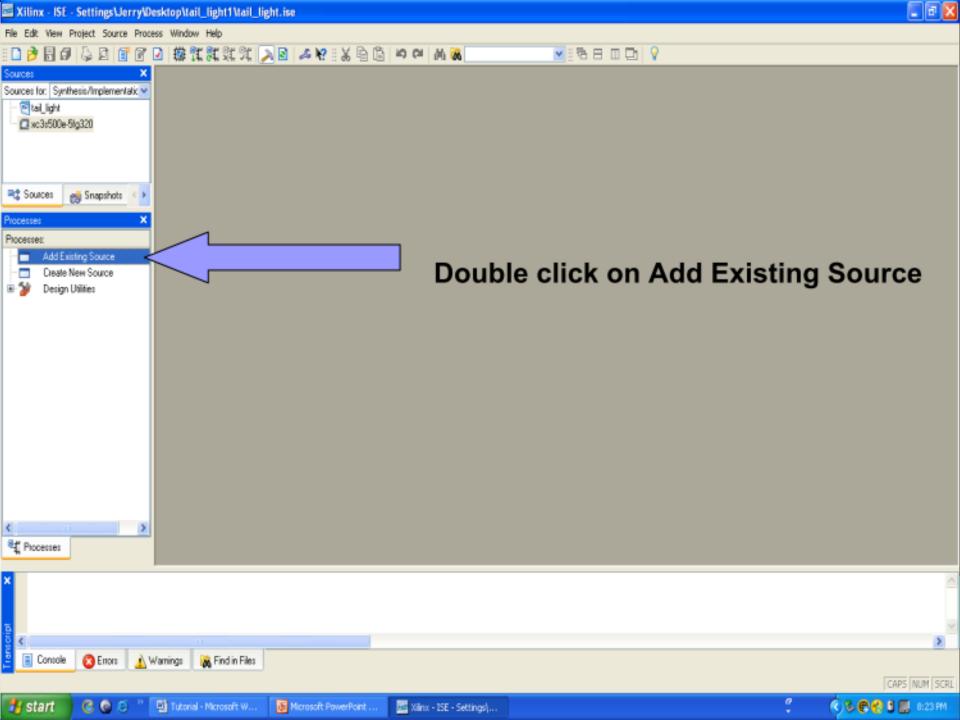

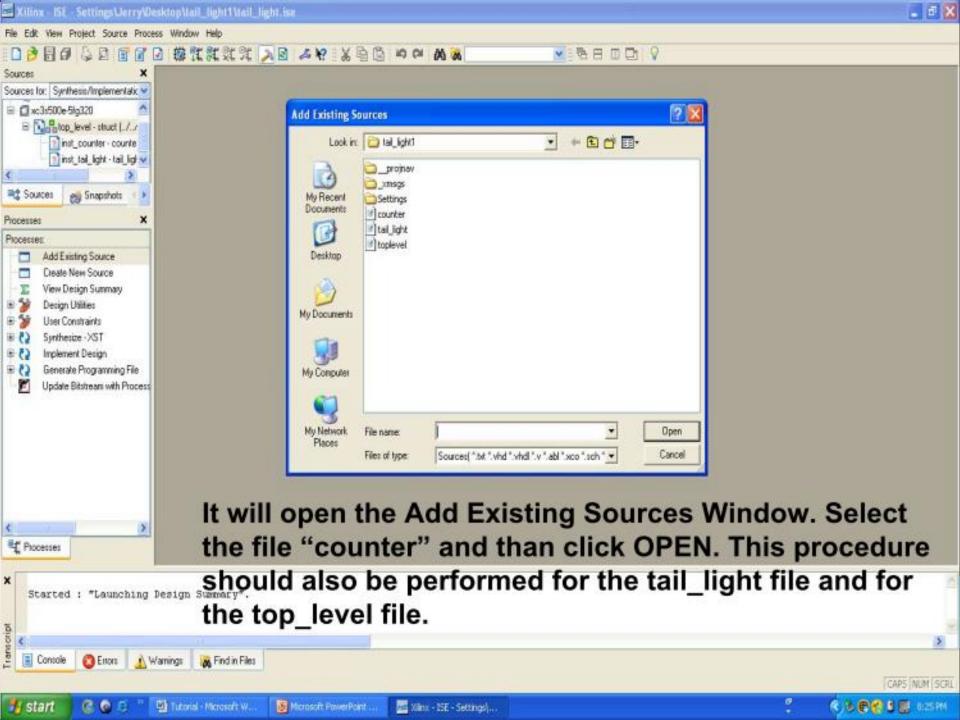

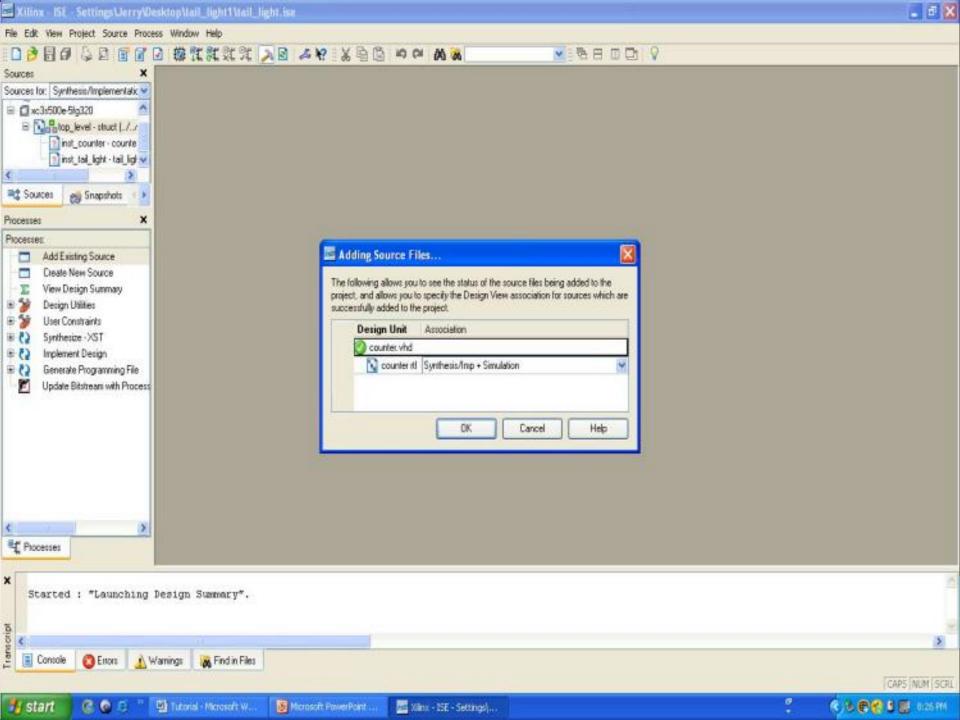

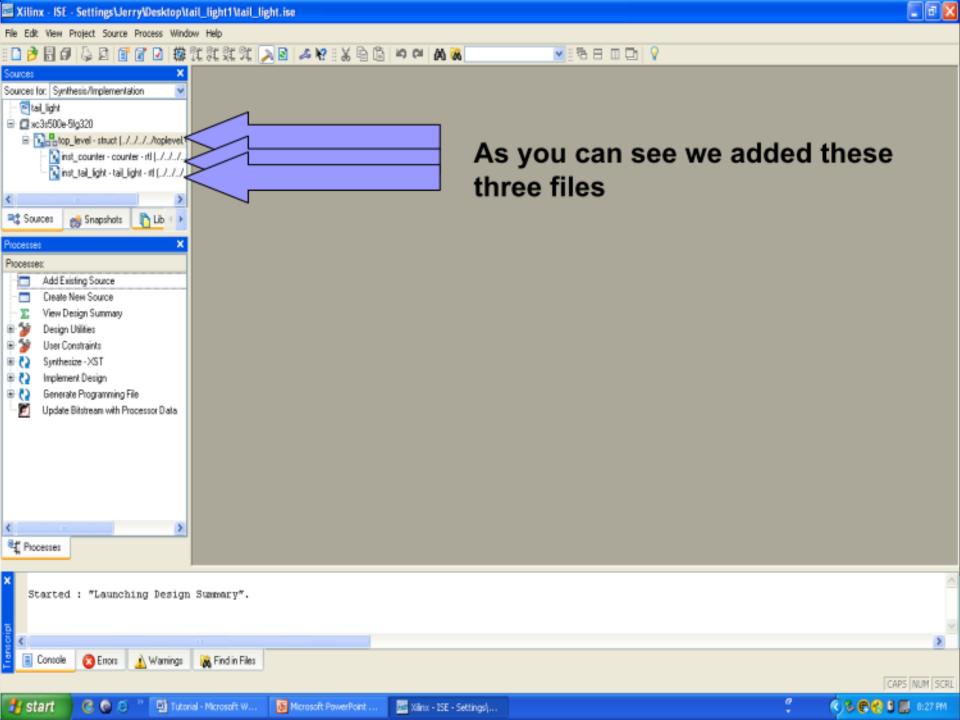

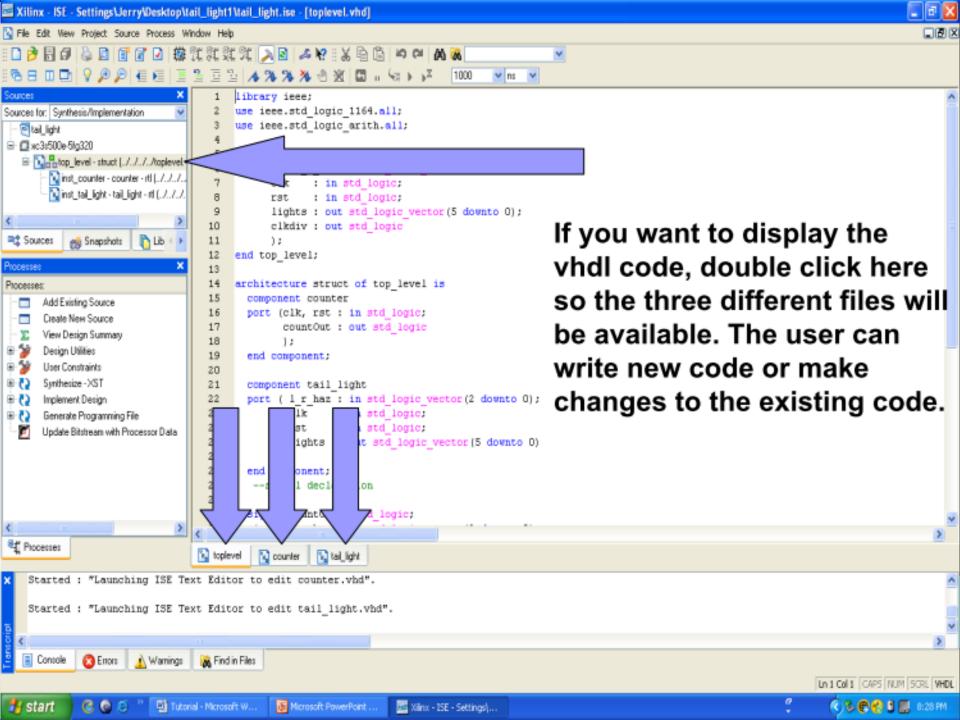

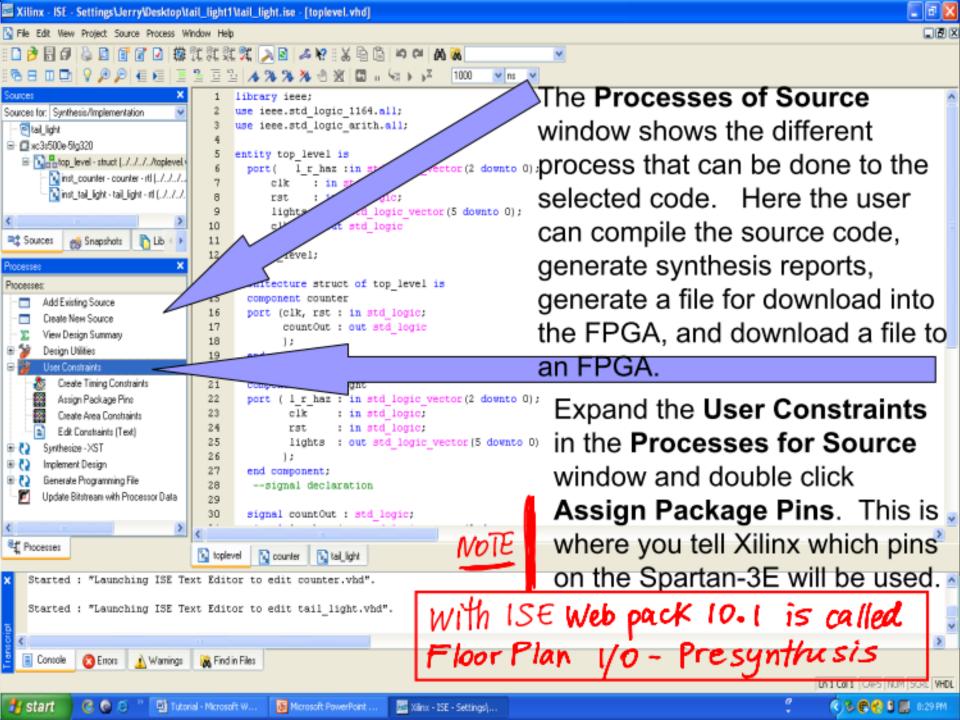

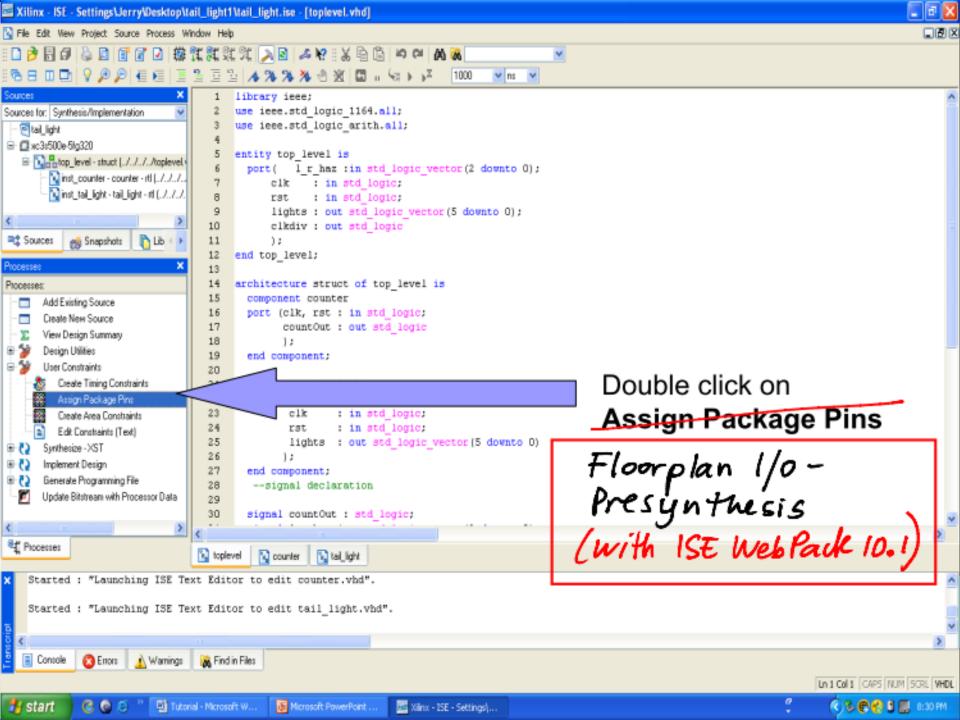

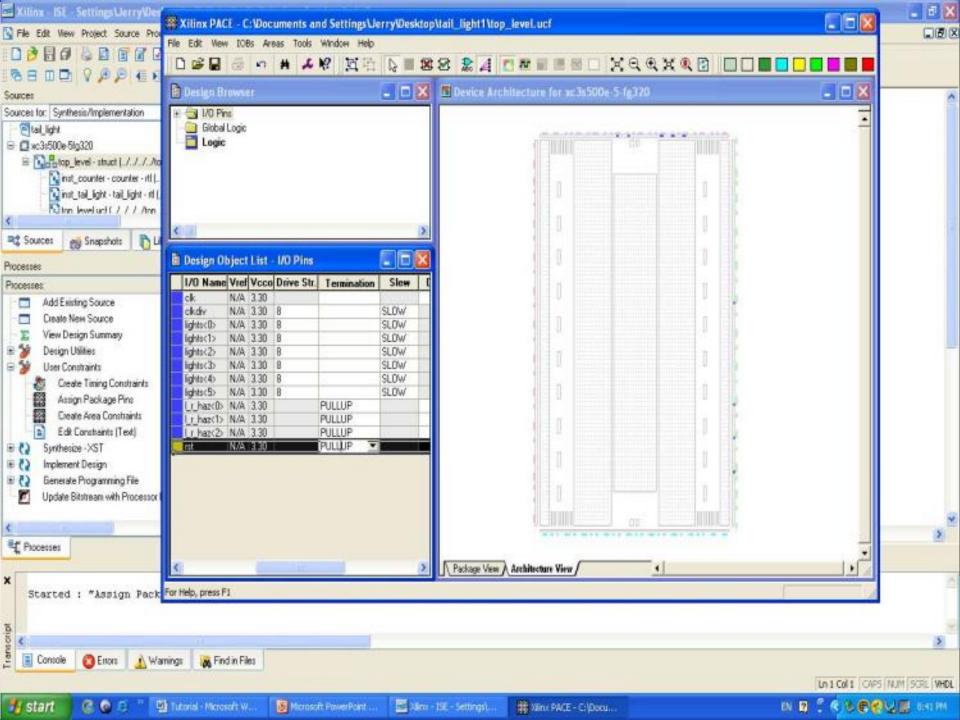

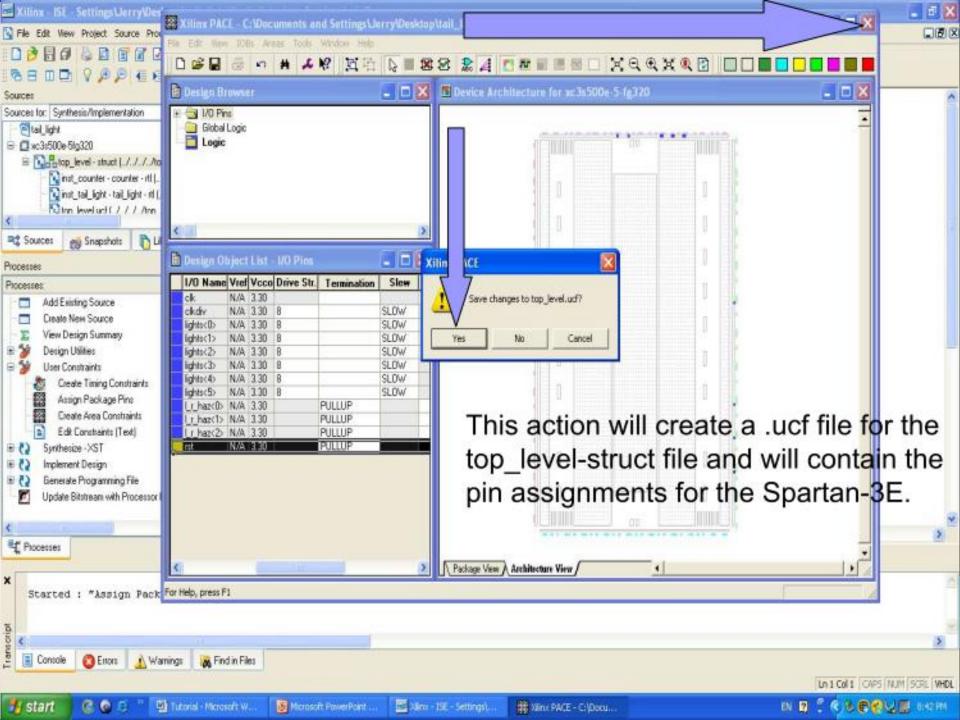

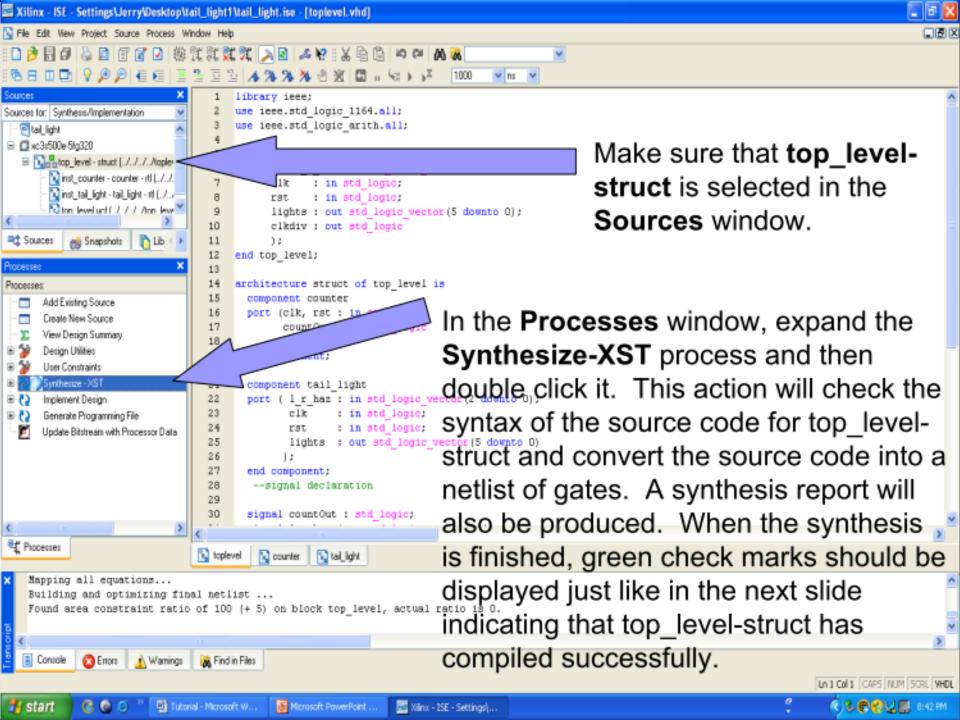

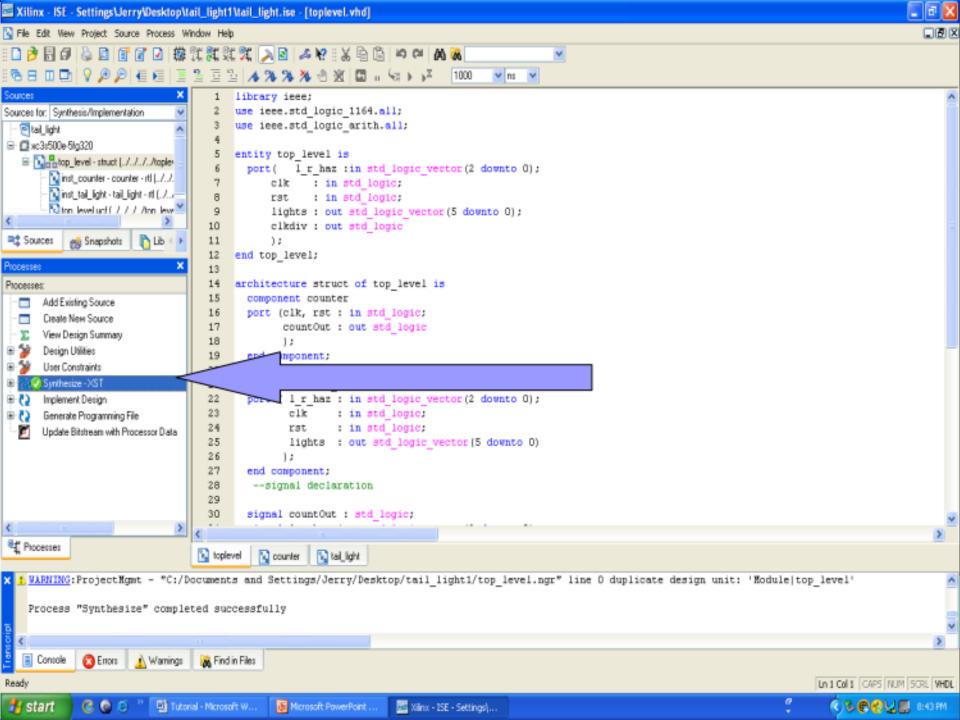

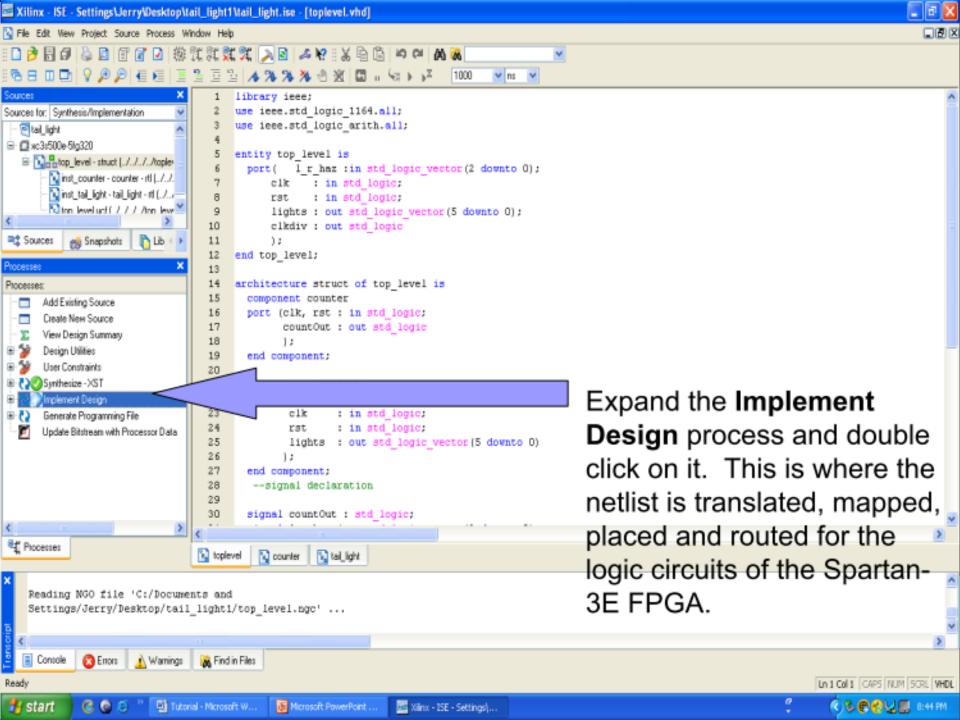

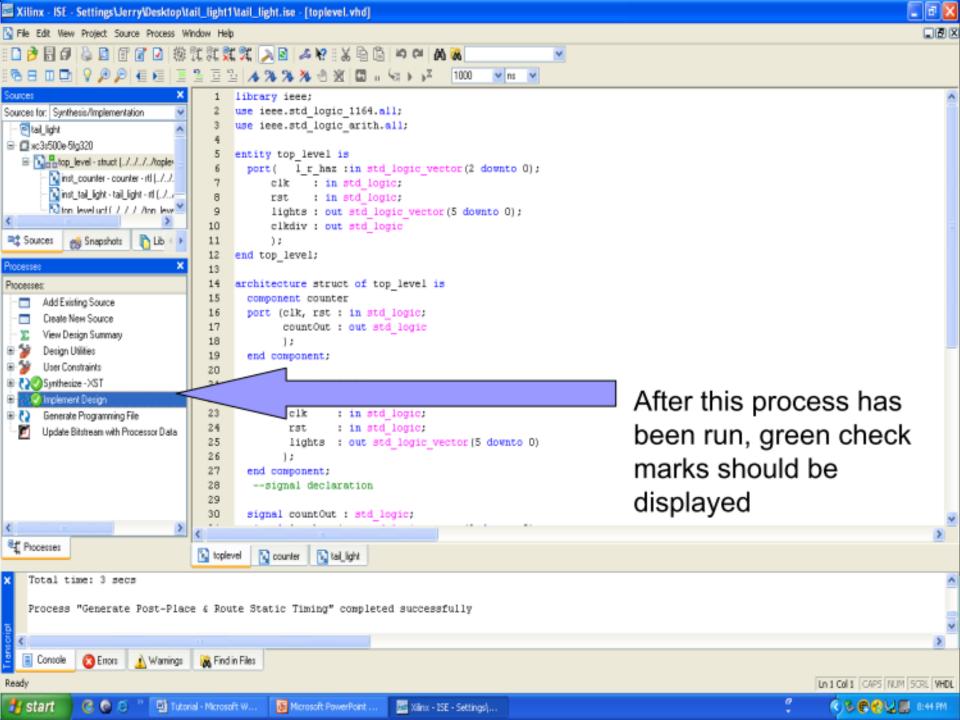

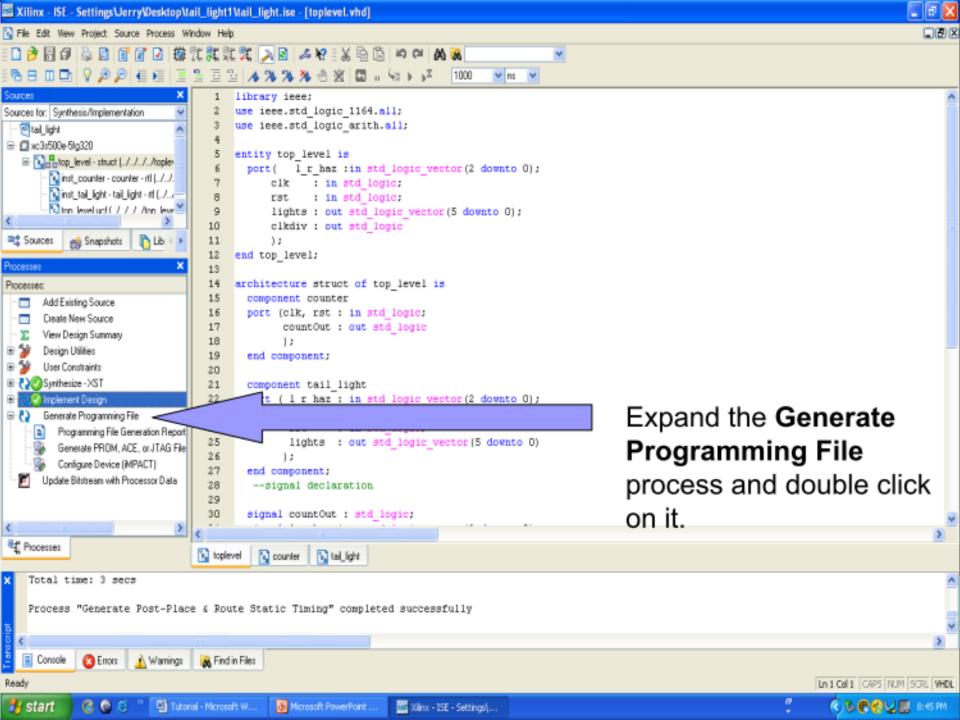

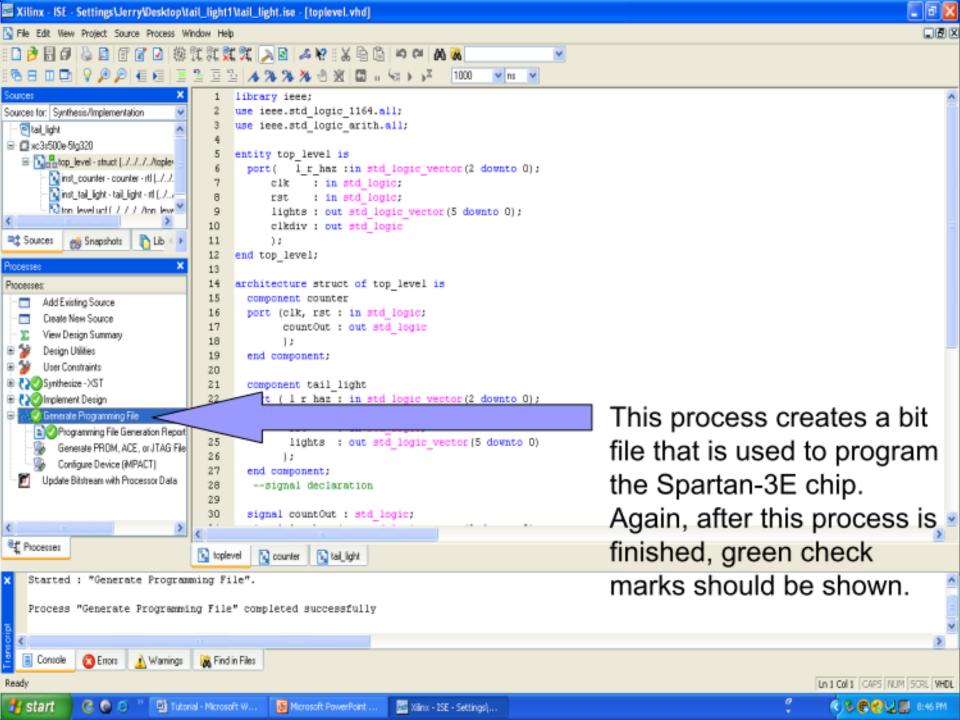

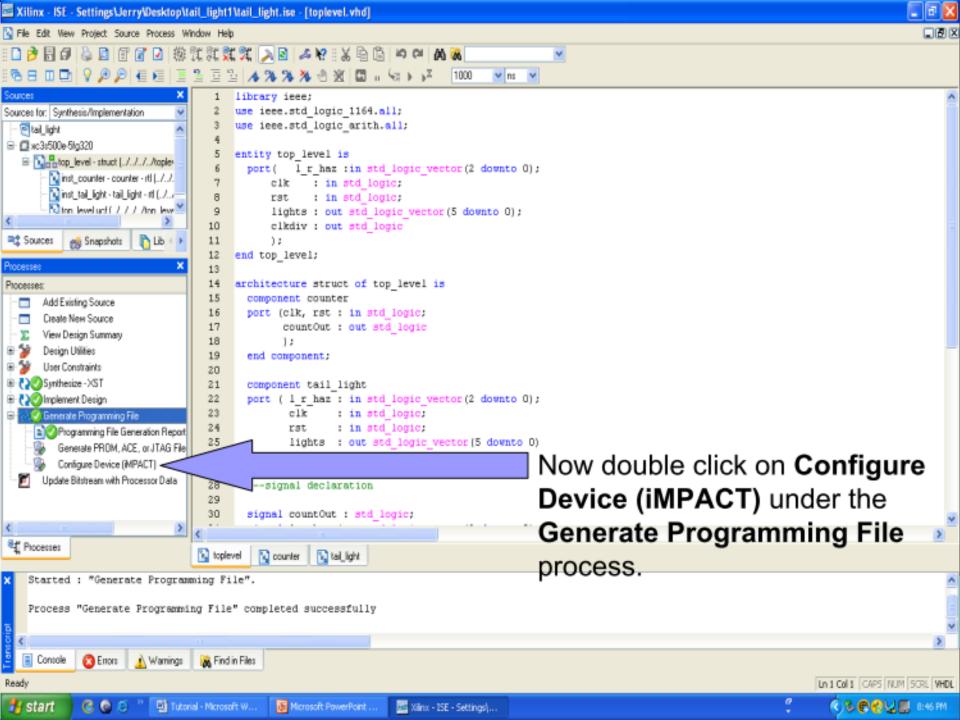

- To have a project ready to program the Spartan 3E FPGA, it was necessary to take a few preliminary steps. First, a project needed to be created in Xilinx. The project was named tail\_light.

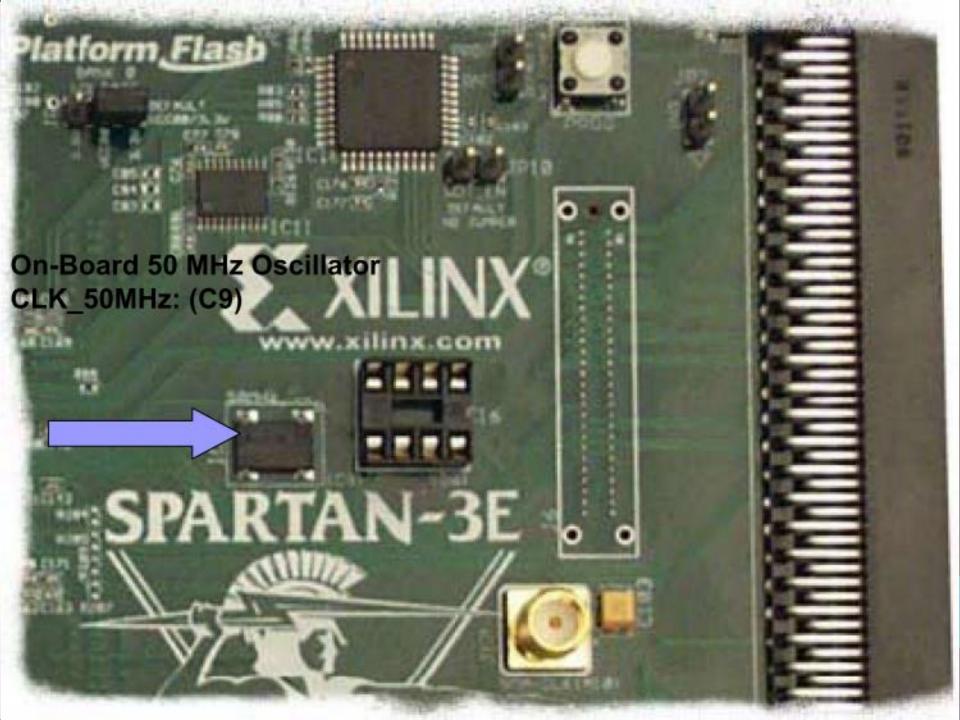

- the board has a 50MHz oscillator (see reference manual); therefore, the clock signal is so fast that the human eye is unable to see the sequence of the flashing lights. As a result, we had to add an additional file called counter.vhd, which will slow the incoming clock down.

- In order for these two files to work together, we had to write the top level.vhd file

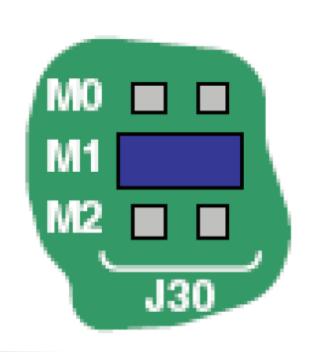

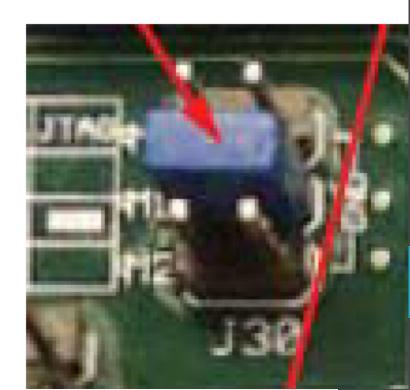

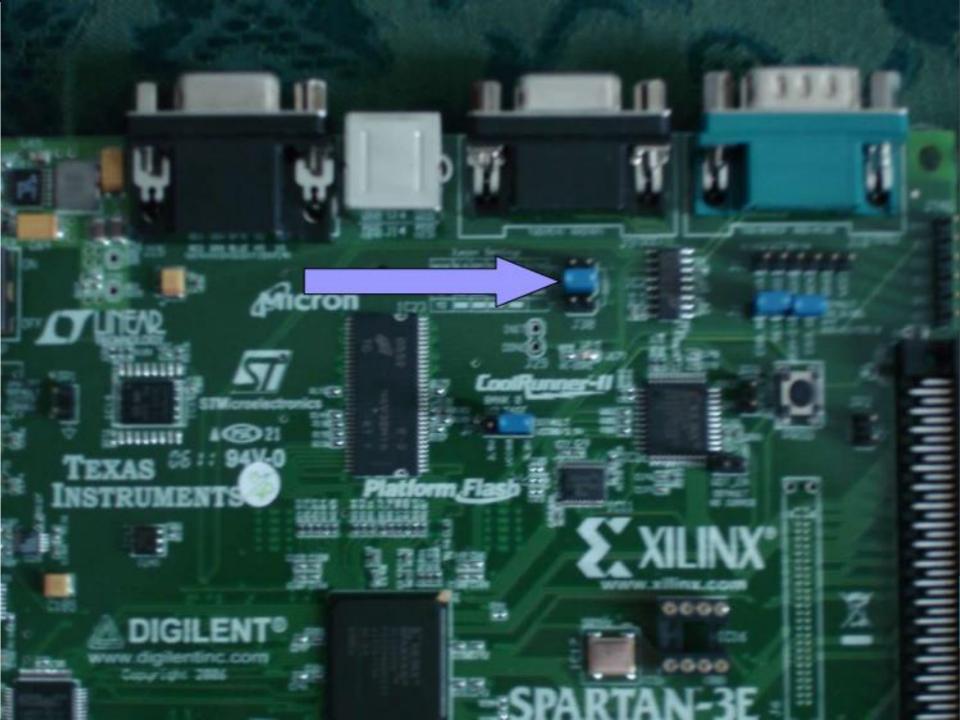

# Spartan-3E Configuration Mode Jumper Settings

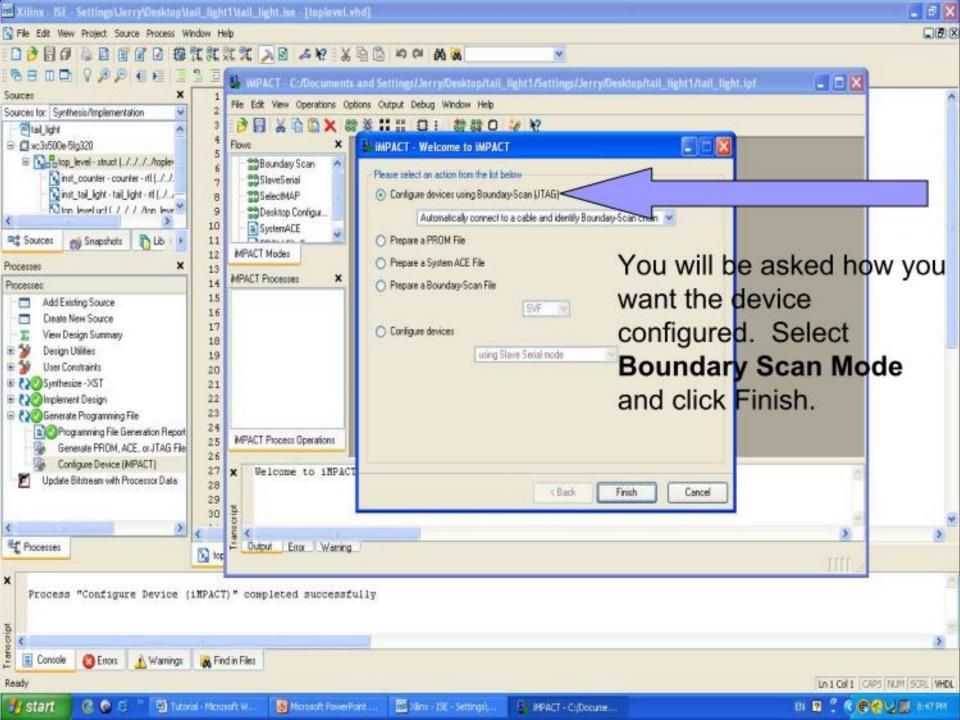

- **Configuration Mode** JTAG

- Download from host via USB JTAG port

#### FPGA CLOCK INPUTS

- Clock Input FPGA Pin Global Buffer Associated DCM

- CLK\_50MHZ C9 GCLK10 DCM\_X0Y1

- CLK\_AUX B8 GCLK8 DCM\_X0Y1

- CLK\_SMA A10 GCLK7 DCM\_X1Y1

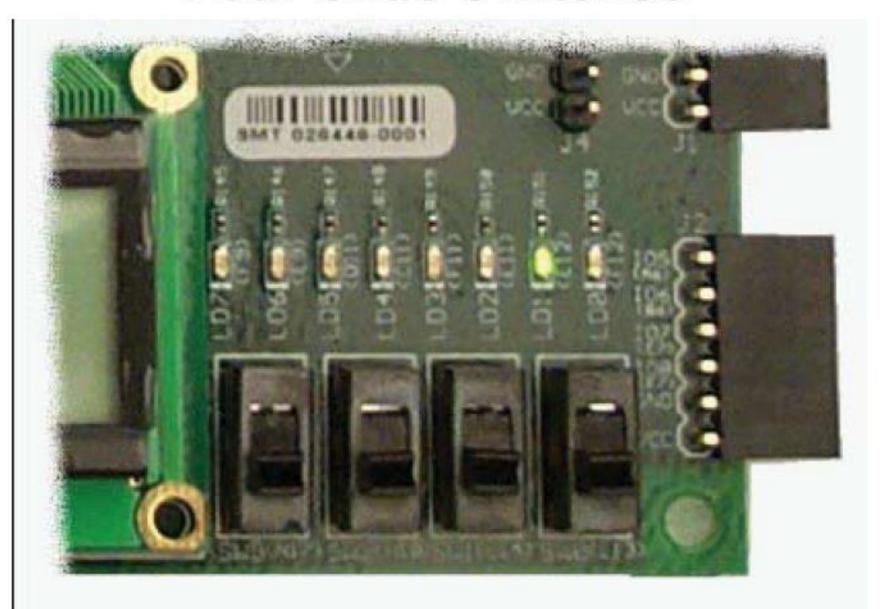

## **Four Slide Switches**

### M

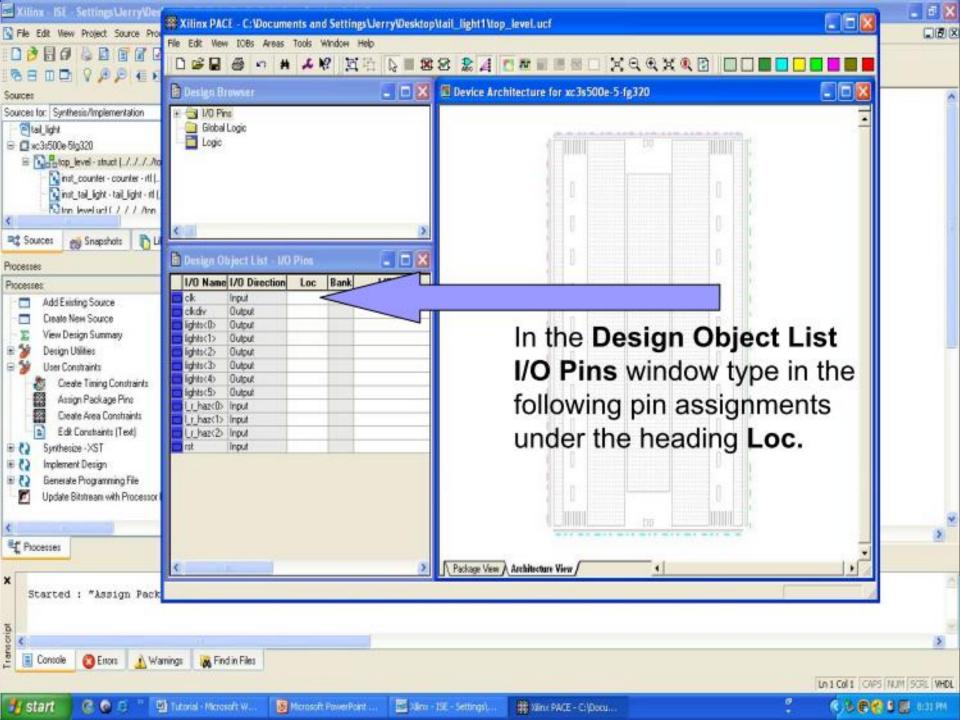

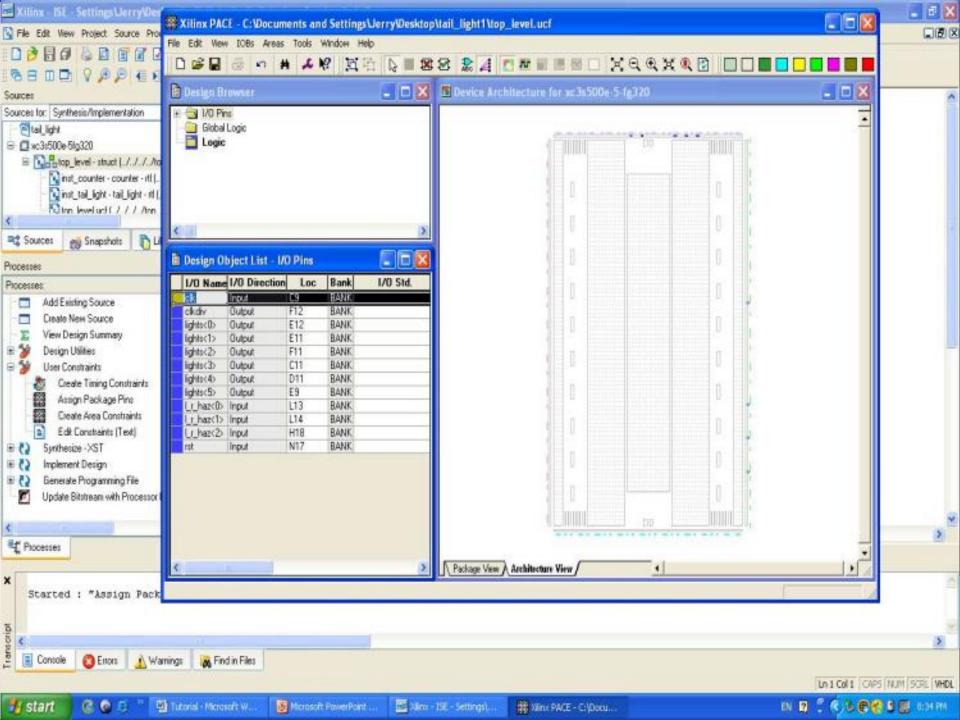

# Pin assignments

- NET "SW<0>" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP;

- NET "SW<1>" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP;

- NET "SW<2>" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP;

- NET "SW<3>" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP;

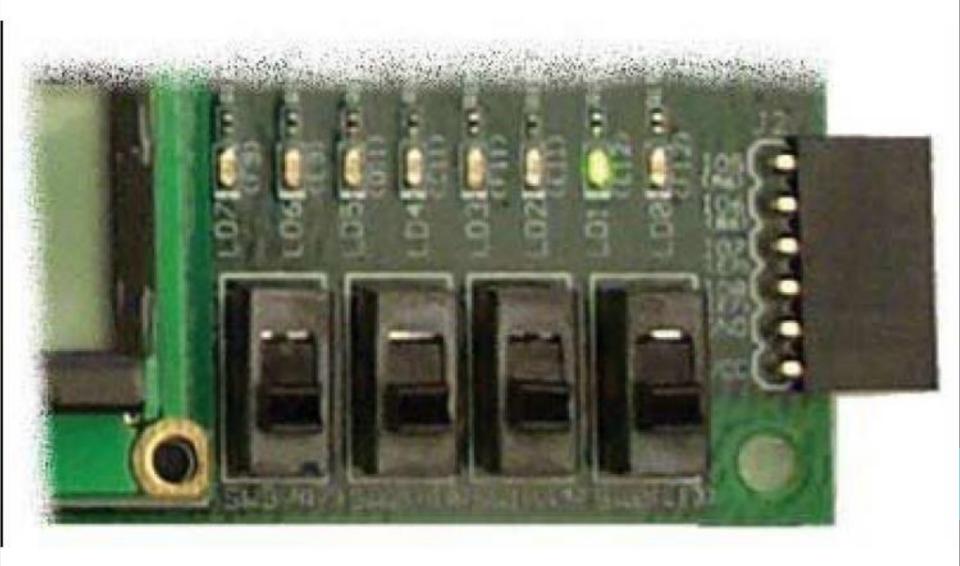

# **Eight Discrete LEDs**

# UCF Constraints for Eight Discrete LEDs

```

NET "LED<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

NET "LED<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;

```

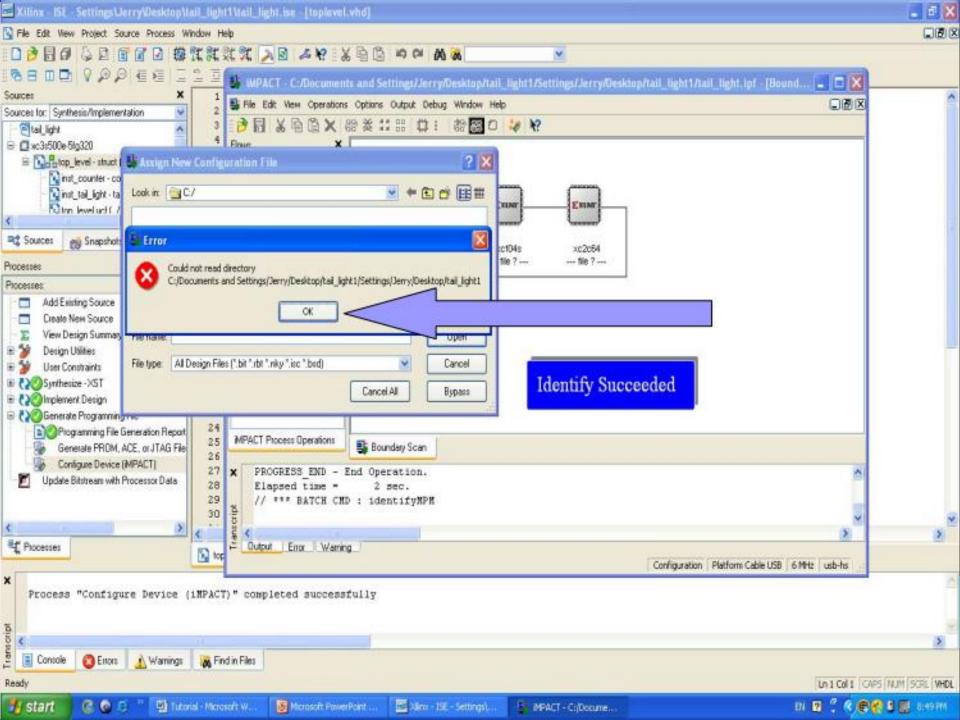

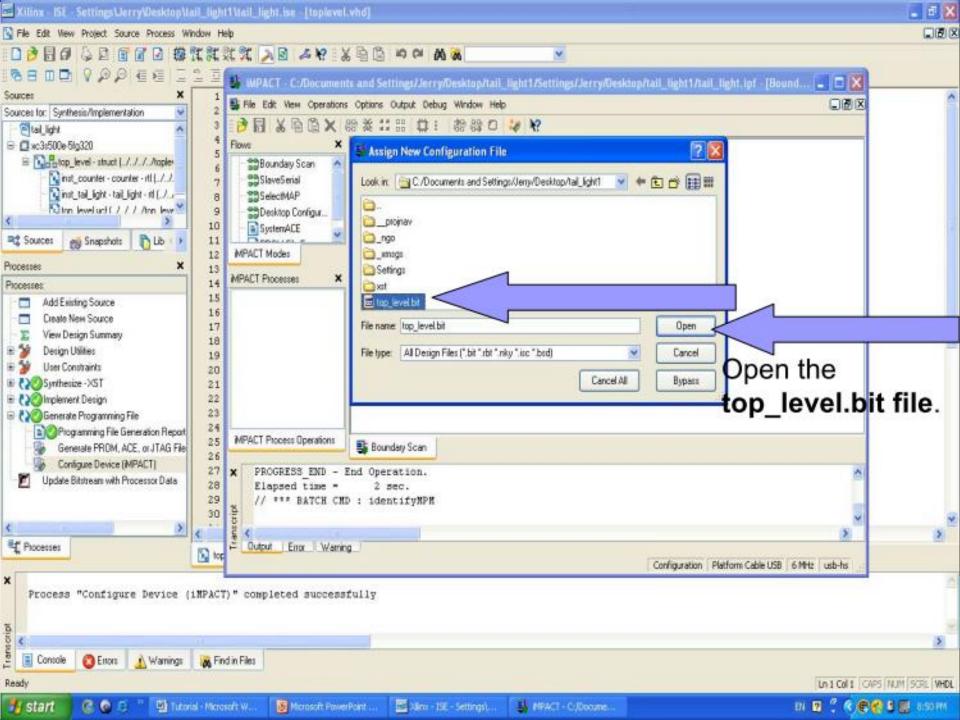

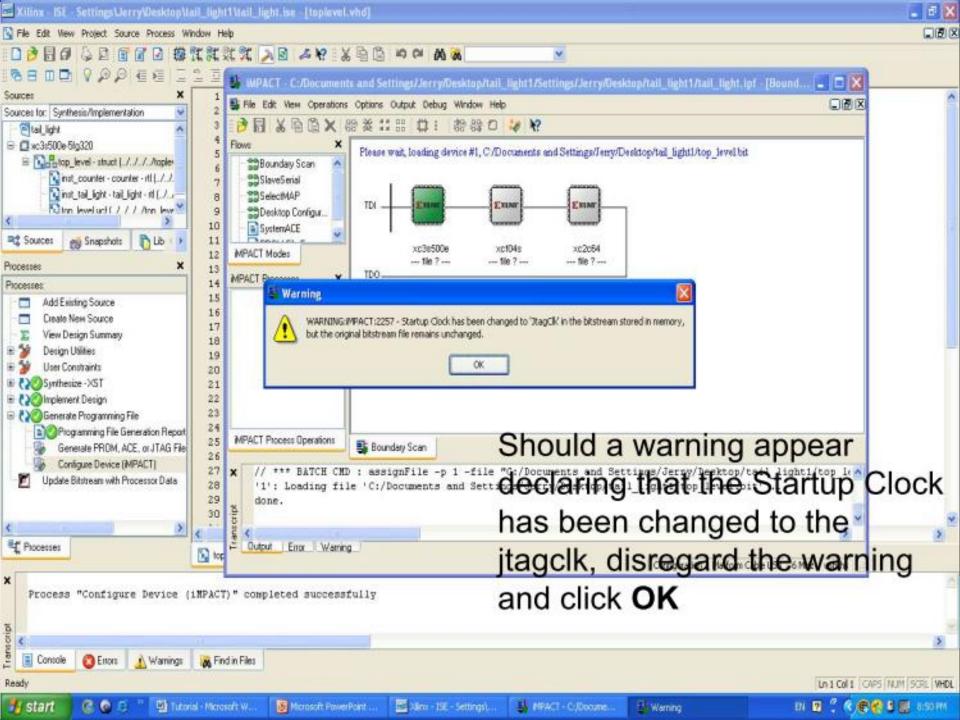

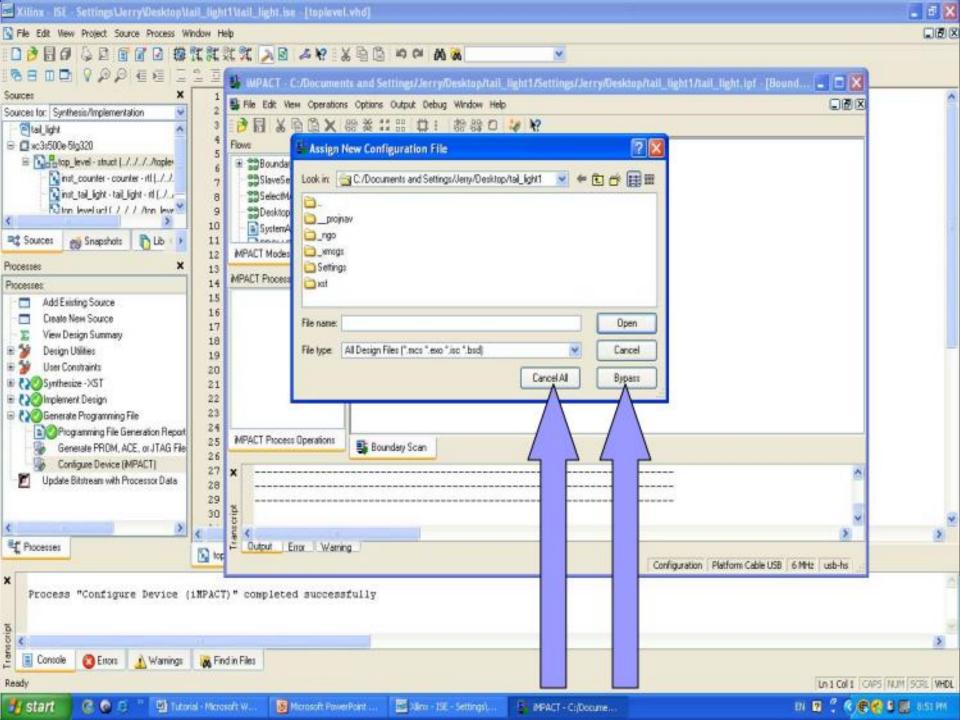

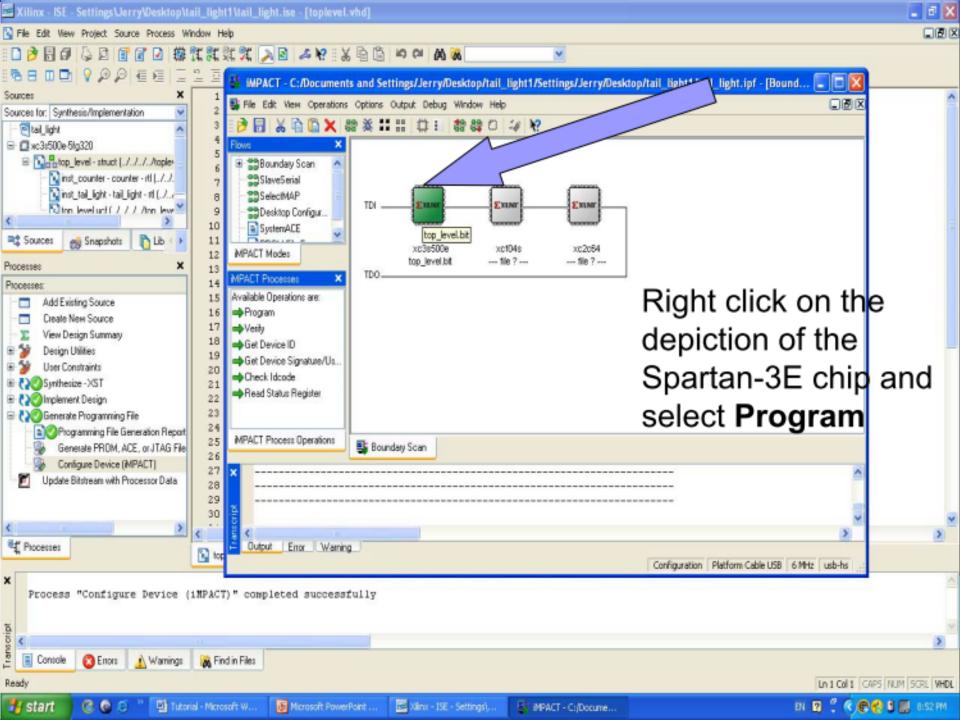

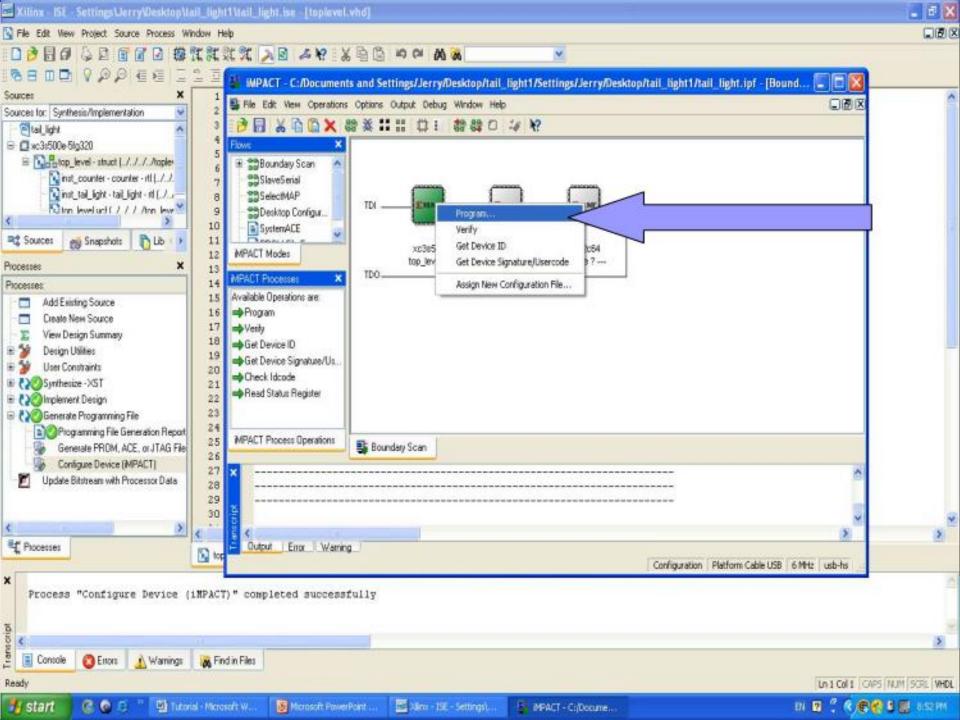

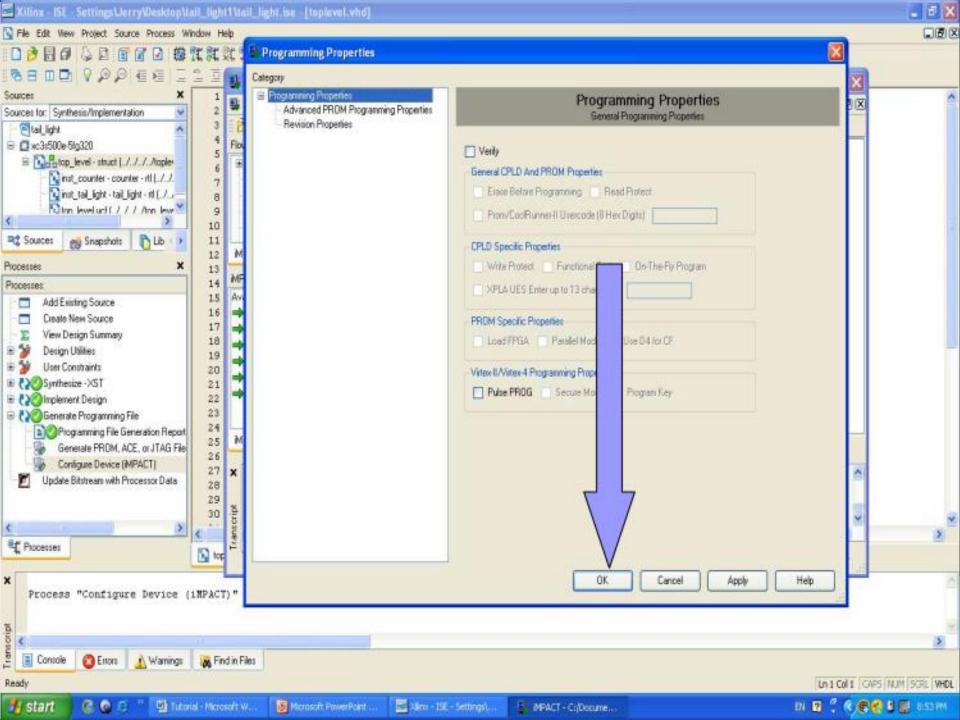

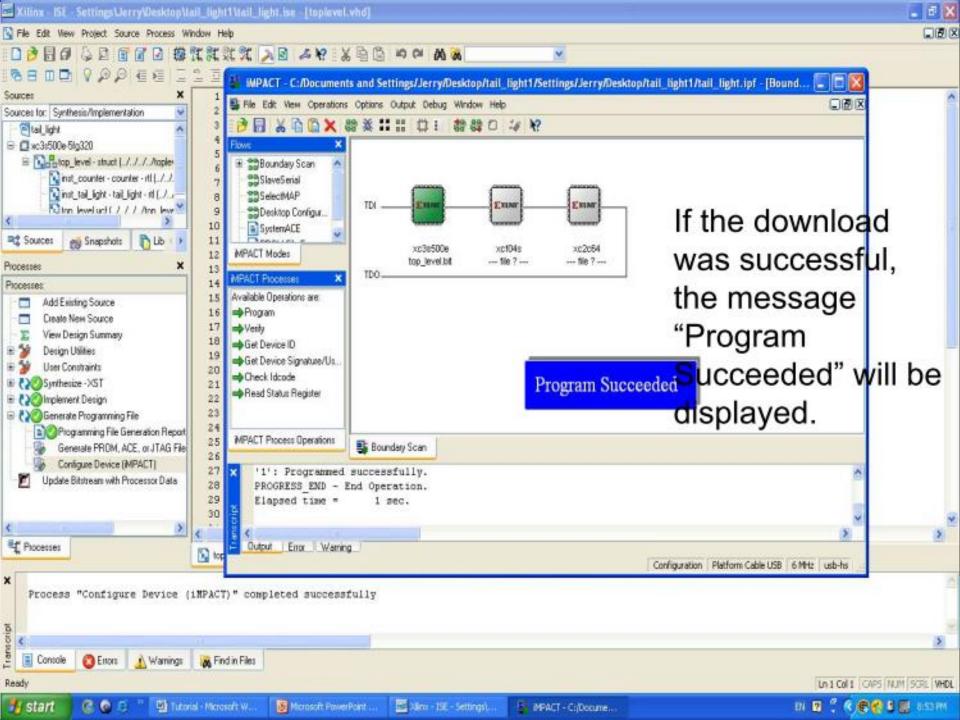

## **FPGA**

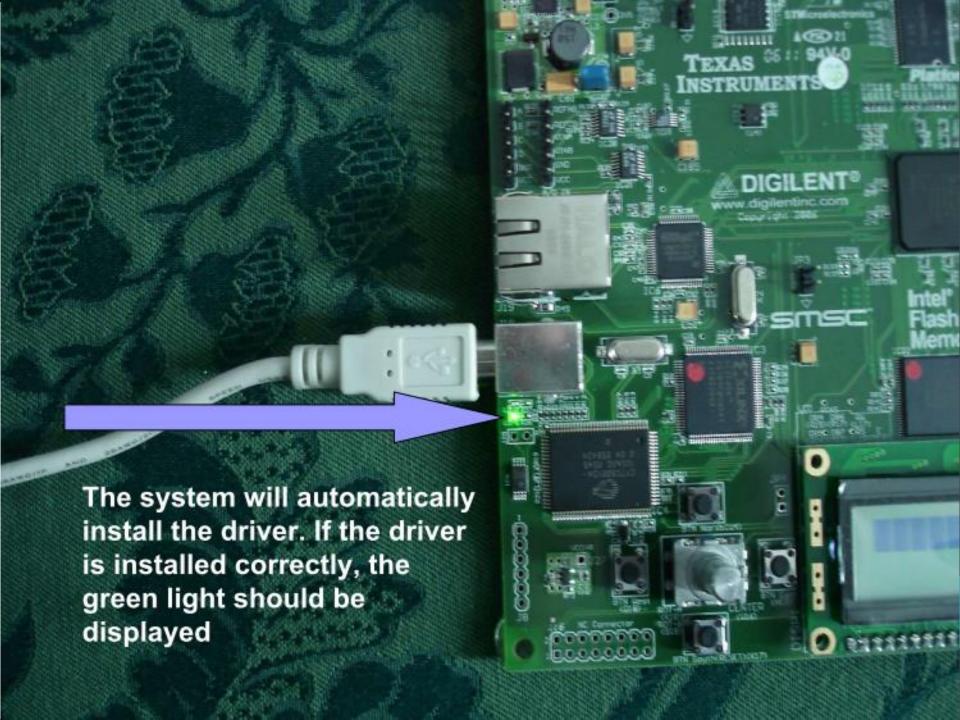

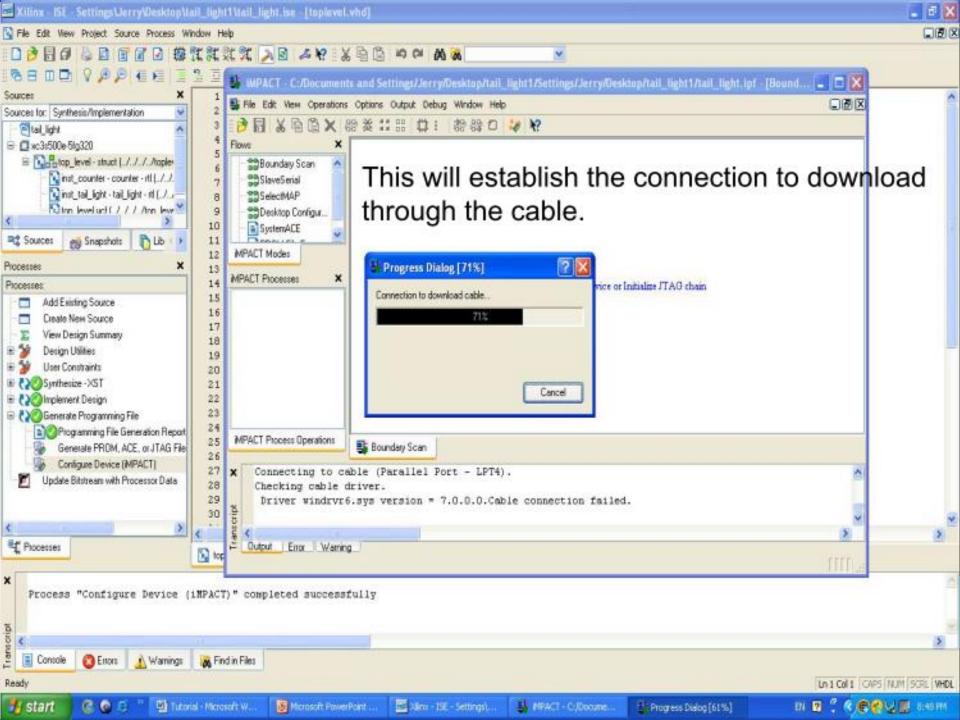

Now you are ready to program the Spartan-3E chip. Plug-in the USB cable to the computer. Connect the FPGA Spartan-3E board to power FIRST, then connect the USB cable to the board. This order must be followed for the Spartan-3E chip to be programmed properly.

## **FPGA Demo**

- For more details, refer to:

- Computer Aided Design of Electronics course lecture notes.

- The VHDL Cookbook, Peter J. Ashenden, 1st edition, 1990.

- The lecture is available online at:

- <a href="http://bu.edu.eg/staff/ahmad.elbanna-courses/12135">http://bu.edu.eg/staff/ahmad.elbanna-courses/12135</a>

- For inquires, send to:

- ahmad.elbanna@feng.bu.edu.eg